Lattice Semiconductor ICE40UP5KSWAEVN SWA-Evaluierungsboard

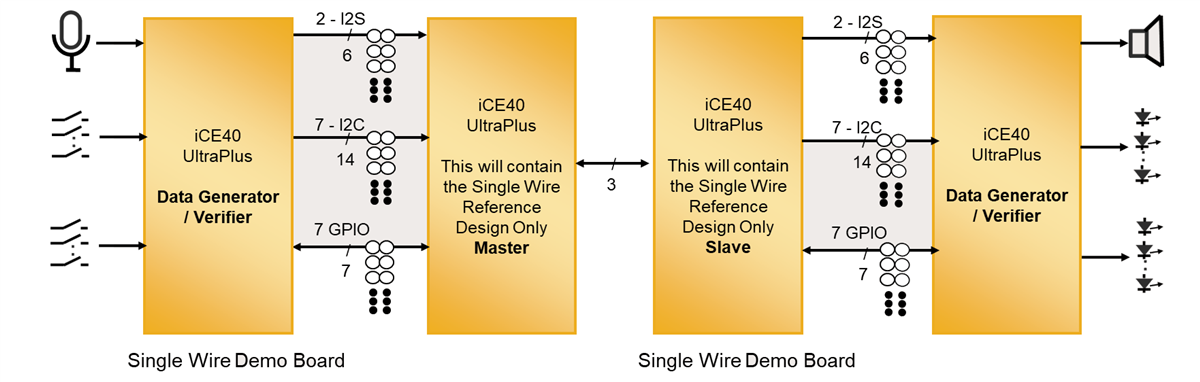

Das Lattice Semiconductor ICE40UP5KSWAEVN Einzeldraht-Aggregations-Evaluierungsboard ist anpassbar und reduziert die Kabel- und Steckverbindergröße bei gleichzeitiger Erhöhung der Zuverlässigkeit. Das ICE40UP5KSWAEVN SWA-Evaluierungsboard enthält zwei Boards zur Demonstration des vollständigen Betriebsdesigns in einer eigenständigen Konfiguration.Das ICE40UP5KSWAEVN SWA-Evaluierungsboard von Lattice unterstützt bis zu 7 aggregierte Kanäle und jeder Kanal kann entweder I2C, I2S oder GPIO sein. Das SWA-Evaluierungsboard bietet eine PCB-Entlastung mit FPGAs für die Signalaggregation und Übertragung über einen einzelnen Draht.

Merkmale

- Keine FPGA-Tool-Kenntnisse erforderlich

- Anpassbar über verfügbares Referenzdesign

- Bis zu 7 Kanäle können aggregiert werden

- Jeder Kanal kann entweder I2C, I2S oder GPIO sein

- Der Board-Satz kann als eigenständige Demonstration oder als In-System-Machbarkeitsnachweis konfiguriert werden

Lieferumfang Kit

- Zwei SWA-Evaluierungsboards

- Zwei Jumper-Drähte

- Zwei Mikro-USB-Kabel

- Kurzanleitung

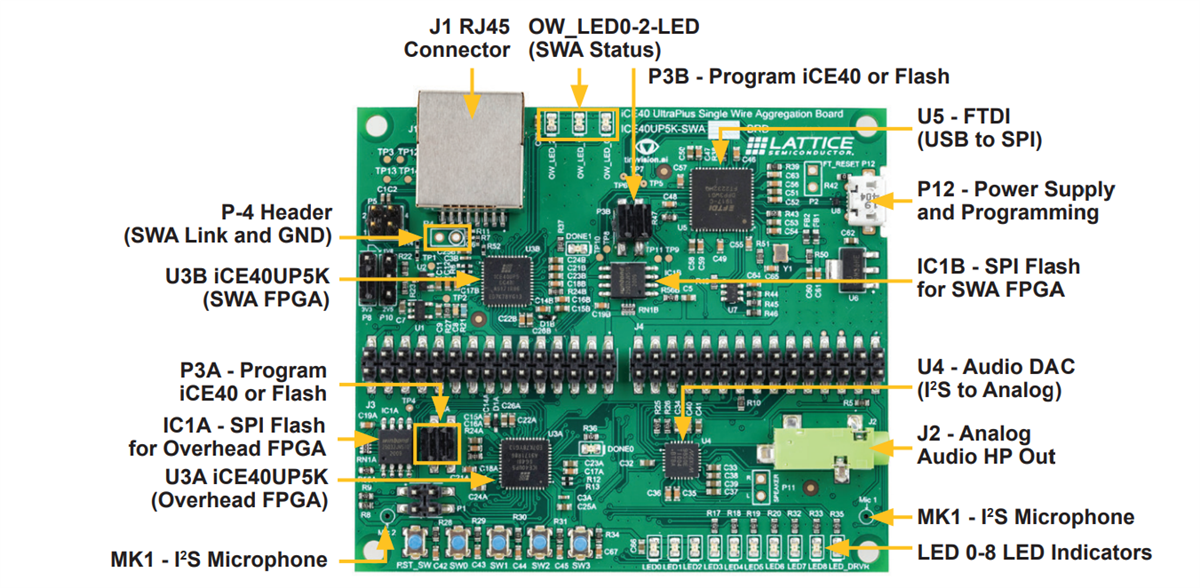

Board-Layout

Blockdiagramm

Übersicht

Videos

Weitere Ressourcen

Veröffentlichungsdatum: 2020-10-06

| Aktualisiert: 2024-05-16