Renesas Electronics 9ZML12x2E Taktpuffer

Die 9ZML12x2E Taktpuffer von IDT sind MUX der 2. Generation mit 2 Eingängen und 12 Ausgängen für Intel Purley und neue Plattformen. Diese Taktpuffer überschreiten die anspruchsvollen DB1200ZL-Leistungsspezifikationen und sind abwärtskompatibel zum 9ZML1232B. Die 9ZML12x2E-Pufferspeicher verwenden stromsparende HCSL-kompatible Ausgänge und Anschlusswiderstände. Zu den Funktionen gehören 9 wählbare SMBus-Adressen, Phase-Locked-Loop (PLL) oder Bypass-Modus, Spreizspektrum-kompatibel und SMBus-Schnittstelle. Diese Taktpuffer bieten zwei konfigurierbare Low-Drift-I2O-Einstellungen, eine für jeden Eingangskanal, um I2O-Tuning für verschiedene Topologien zu ermöglichen. Typische Applikationen umfassen Server, Speicher, Netzwerke und PCI-Express der Gen. 1–4 oder QPI-/UPI-Applikationen.Merkmale

- 2 konfigurierbare Low-Drift-I2O-Verzögerungen von bis zu 2,9 ns halten die Transportverzögerung

für verschiedene Topologien aufrecht - LP-HCSL-Ausgänge eliminieren 24 Widerstände (9ZML1232E)

- LP-HCSL-Ausgänge mit ZAus = 85 Ω beseitigen 48 Widerstände

(9ZML1252E) - 9 auswählbare SMBus-Adressen für mehrere Geräte, die das gleiche SMBus-Segment teilen

- Separate VDDIO für Ausgänge ermöglicht maximale Energieeinsparungen

- Phasenregelkreis- oder Bypass-Modus kann eingehenden Takt dejittern

- PCIe-Taktungsarchitekturen unterstützen:

- Gleichtaktsysteme (CC)

- Separate Reference No Spread (SRNS)

- Separate Reference Independent Spread (SRIS)

- Hardware- oder Software-wählbare PLL-BW minimiert Jitter

spitzen in nachgelagerten PLLs - Spreizspektrum-kompatible Schienen verteilen den Eingangstakt für

EMI-Reduzierung - Die SMBus-Schnittstellensoftware kann Geräteeinstellungen ohne Hardwareänderungen ändern

- 10 mm x 10 mm 72-QFN-Gehäuse mit einem kleinen Footprint

- Ausgabefunktionen:

- 12 stromsparende HCSL-Ausgangspaare (LP-HCSL) (9ZML1232E)

- 12 stromsparende HCSL-Ausgangspaare (LP-HCSL) mit 85 Ω

ZOut (9ZML1252E)

Technische Daten

- <50 ps Zyklus-zu-Zyklus-Jitter

- <50 ps Versatz zwischen Ausgängen

- Feste Eingangs-Ausgangs-Verzögerung bei 0 p/s

- <50 ps Eingang-Ausgang- Verzögerungsabweichung

- Phasen-Jitter PCIe Gen. 4 < 0,5 ps RMS

- Phasenjitter QPI/UPI ≥9,6 GB/s <0,1 ps RMS

Applikationen

- Server

- Speicherung

- Netzwerke

- Solid State Drives (SSDs)

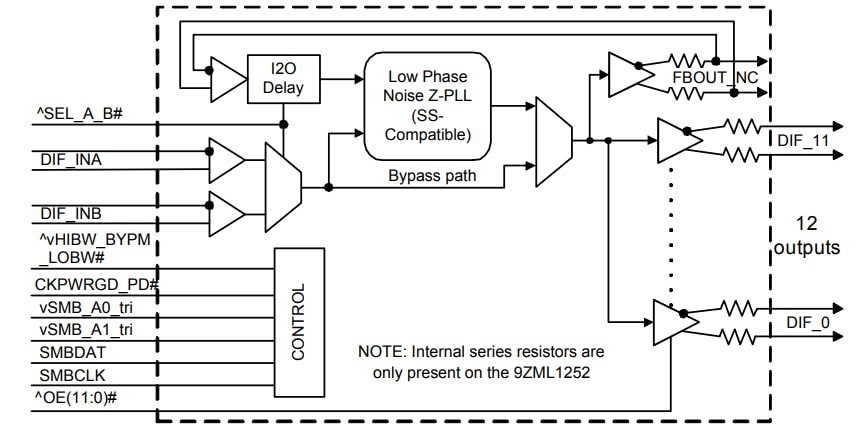

Blockdiagramm 9ZML12x2E Taktpuffer

View Results ( 4 ) Page

| Teilnummer | Datenblatt | Beschreibung | Betriebsversorgungsstrom |

|---|---|---|---|

| 9ZML1252EKILF |  |

Taktsignalpuffer 9ZML1252E DB1200ZL MUX DERIV LITE | 22 mA |

| 9ZML1232EKILF |  |

Taktsignalpuffer 9ZML1232E DB1200ZL MUX DERIV | 13 mA |

| 9ZML1232EKILFT |  |

Taktsignalpuffer 9ZML1232E DB1200ZL MUX DERIV | 13 mA |

| 9ZML1252EKILFT |  |

Taktsignalpuffer 9ZML1252E DB1200ZL MUX DERIV LITE | 22 mA |

Veröffentlichungsdatum: 2018-05-28

| Aktualisiert: 2023-01-23