BittWare XUP-P3R FPGA-Beschleunigerkarte

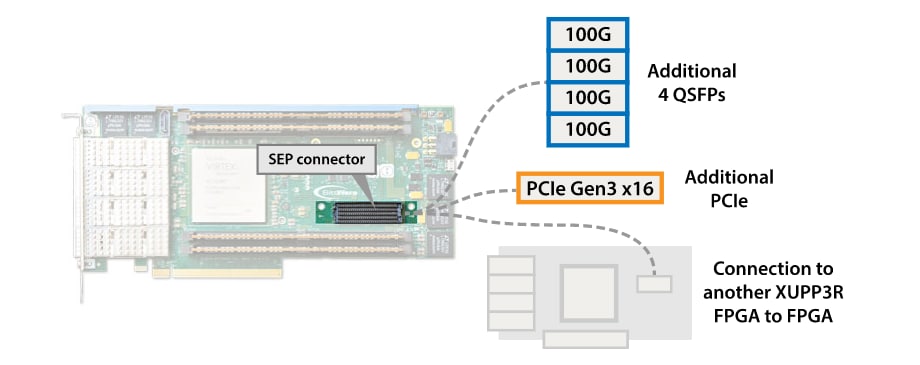

Die BittWare XUP-P3R FPGA-Beschleunigerkarte ist eine 3/4-Längen-PCIe-x16-Karte, die auf dem Xilinx Virtex UltraScale + FPGA basiert, das eine hohe Leistungsfähigkeit, eine hohe Bandbreite und eine reduzierte Latenz für Systeme liefert, die einen massiven Datenfluss und eine Paketverarbeitung erfordern. Die XUP-P3R Karte bietet umfangreiche Speicherkonfigurationen, einschließlich Unterstützung für bis zu 512 GB, anspruchsvolle Takt- und Timing-Optionen und vier QSFP-Käfige auf dem Frontpanel, die jeweils 100 GBit/s (4x25) und 100 GbE unterstützen. Der serielle Erweiterungsanschluss (SEP) ermöglicht die Erweiterung des XUPP3R für einen zusätzlichen PCIe Gen3 x16 Steckplatz, zusätzliche 4 QSFPs oder eine Verbindung zwischen zwei XUPP3Rs. Die XUP-P3R FPGA-Beschleunigerkarte von BittWare enthält einen Board-Management-Controller (BMC) für eine fortschrittliche Systemüberwachung und Vereinfachung der Integration und Verwaltung der Plattform. Der XUP-P3R eignet sich hervorragend für Rechenzentrumsapplikationen, einschließlich Netzwerkverarbeitung und Sicherheit, Beschleunigung, Speicherung, Übertragung und SigInt.Merkmale

- Umfangreiche Speicherkonfigurationen, bis zu 512 GB DDR4

- Integriert BMC für eine erweiterte Systemüberwachung

- 4 x 100 GbE über 4 QSFP28

- 2,5 Millionen LCs FPGA von Xilinx bis zu VU9P

- Vereinfacht die Integration und Verwaltung der Plattform

Technische Daten

- FPGA

- Virtex UltraScale+ VU9P

- Core-Geschwindigkeitsklasse – 2

- On-Board-Flash-Speicher für das Hochfahren von FPGA

- Externer Speicher

- 4 DIMM-Positionen, die jeweils Folgendes unterstützen:

- Bis zu 128 GBytes DDR4 x72 mit ECC

- Bis zu 576 MBits Dual-QDR-II+ x 18 (2 unabhängige 288-MBit-Banken)

- 4 DIMM-Positionen, die jeweils Folgendes unterstützen:

- x16 Gen3 Host-Schnittstelle direkt zum FPGA

- Mikro-USB-2.0-Anschlüsse für Debugging und Programmierung von FPGA und Flash

- Serieller Erweiterungsanschluss (SEP)

- Erweiterungsschnittstelle zu FPGA über 20 x GTY-Transceiver (optional; erfordert einen zweiten Steckplatz)

- 14 x GPIO-Signale zum FPGA

- Boardmanagement-Controller

- Spannungs-, Strom- und Temperaturüberwachung

- Leistungssequenzierung und Reset

- Upgrades vor Ort

- FPGA-Konfiguration und -Steuerung

- Taktkonfiguration

- I2C-Bus-Zugang

- USB 2,0

- Spannungsüberlagerungen

- Spannungs-, Strom- und Temperaturüberwachung

- FPGA-Entwicklung

- QSFP-Käfige

- 4 QSFP28-Käfige (zQSFP) auf dem Frontpanel, die direkt mit dem FPGA über 16 Transceiver verbunden sind

- Unterstützen jeweils 100 GbE, 40 GbE, 4 x 25 GbE oder 4 x 10 GbE und können für 400 GbE kombiniert werden

- Kühlung

- Aktiver Lüfter mit doppelter Breite und Kühlkörper – Standard

- Passiver Kühlkörper mit doppelter Breite – optional

- Erweiterte passive Kühlung mit doppelter Breite über Wärmerohre – optional

- Elektrische Daten

- On-Board-Leistung, die von einem 12-V-PCIe-Steckplatz und einem AUX-Steckverbinder (6-Pin) abgeleitet wird

- Die Verlustleistung ist applikationsabhängig

- +5 °C bis +35 °C Betriebstemperaturbereich

- Formfaktor

- 3/4-langes PCIe-Board mit zwei Steckplätzen und Standardhöhe

- 9,4 Zoll x 4,37 Zoll

- Applikationsentwicklung

- HDL/Verilog

- BittWorks II-Toolkit – Host-, Befehls- und Debug-Tools für die BittWare-Hardware

- Xilinx Vivado Design-Suite

- OpenCL – Xilinx SDAccel-Entwicklungsumgebung, SDAccel-Plattformfreigabe und vorgefertigte Beispiele für XUP-P3R

- HDL/Verilog

Compliances

• FCC (USA) 47CFR15.107 / 47CFR15.109

• CE (Europe) EN 55032:2015/A11:2020 / EN55024:2010 / EN 55035:2017 / EN 61000-3-2:2014 / EN 610003-3:2013

• UKCA (United Kingdom) BS EN 55032:2012/AC:2013 / BS EN55024:2010 / BS EN 55035:2017 / BS EN 61000-3-2:2014 / BS EN 610003-3:2013

• ICES (Canada) ICES-003 issue 7

• Safety objectives referred to in Article 3 and set out in Annex I of DIRECTIVE 2014/35/EU have been fulfilled

• RoHS compliant to the 2011/65/EU + 2015/863 directive

Videos

Formfaktor – Vergleichsdiagramm

Kühloptionen

SEP-Module – Diagramm

Blockdiagramm

Infographic

Veröffentlichungsdatum: 2020-06-11

| Aktualisiert: 2025-10-15