Analog Devices Inc. ADF4383 Fraktional-N-Phasenregelschleifen (PLLs)

Analog Devices ADF4383 Fraktional-N-Phasenregelschleifen (PLLs) sind leistungsstarke Fractional-N-Phasenregelschleifen (PLL) mit extrem geringem Jitter und integriertem spannungsgesteuerten Oszillator (VCO). Diese eignen sich ideal für die lokale Oszillator (LO)-Generierung für 5 G Applikationen oder Daten Wechselrichter Uhr-Applikationen. Der Hochleistungs-PLL verfügt über eine Gütezahl von -239dBc/Hz, geringes 1/f-Rauschen und eine hohe PFD-Frequenz von 625 MHz im Integer-Modus, wodurch ein extrem geringes In-Band-Rauschen und integrierter Jitter erreicht werden kann. Der ADF4383 kann Frequenzen in einem GrundoktavBereich von 10 GHz bis 20 GHz erzeugen, wodurch die Notwendigkeit subharmonischer Filter entfällt. Die Ausgangsteiler auf dem ADF4383 ermöglichen die Generierung eines vollständigen Ausgangsfrequenzbereichs von 625 MHz bis 20 GHz.Die ADF4383 richtet seinen Ausgang automatisch an der Eingabereferenz-Edge für mehrere Datenwandler-Taktgeberapplikationen aus, indem sie den Ausgangsteiler in die PLL-Rückkopplungsschleife einbezieht. Für Applikationen, die eine deterministische Verzögerung oder Verzögerungsanpassungsfähigkeit erfordern, wird eine programmierbare Referenz auf die Ausgabeverzögerung mit einer Auflösung von < 1="" ps="" bereitgestellt.="" die="" referenz="" für="" die="" anpassung="" der="" ausgangsverzögerung="" über="" mehrere="" bauteile="" und="" über="" die="" temperatur="" hinweg="" ermöglicht="" eine="" vorhersehbare="" und="" präzise="">

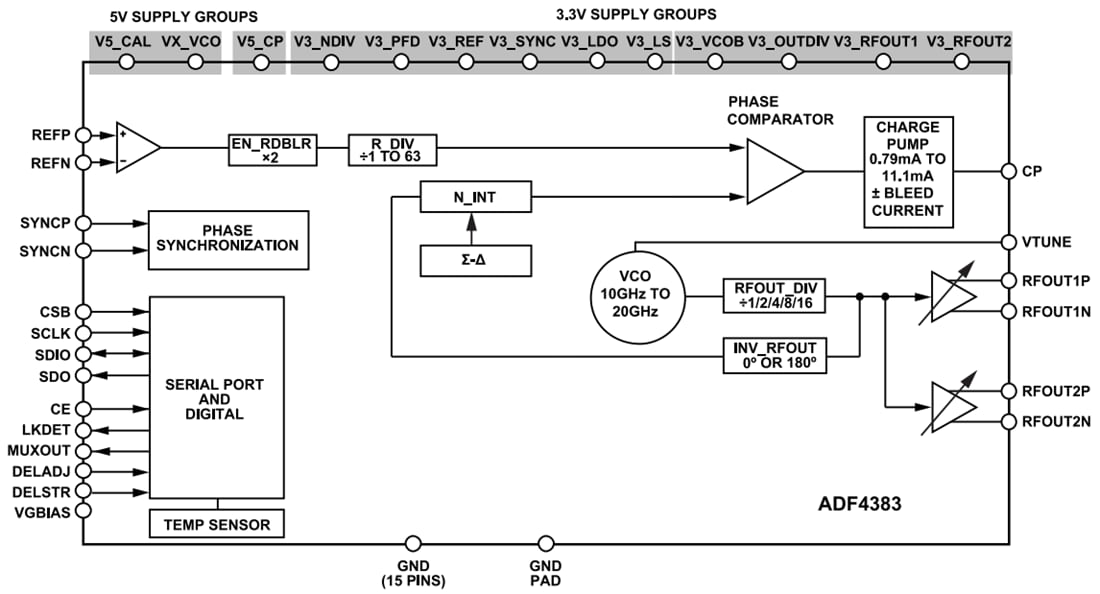

Die Einfachheit des ADF4383 Blockdiagramms von Analog Devices verkürzt die Entwicklungszeit. Es verfügt über eine vereinfachte Registerzuordnung für die serielle Peripherieschnittstelle (SPI), einen externen SYNC-Eingang und eine wiederholbare Multichip-Ausrichtung im Ganzzahl- und Bruchzahl-Modus.

Merkmale

- Grundlegender VCO-Frequenzbereich von 10 GHz bis 20 GHz

- Verbesserung des VCO-Phasenrauschens um bis zu 3 dB im Vergleich zum ADF4382

- Integrierter RMS-Jitter bei 20 GHz = 18 fs (Integrations-Bandbreite: 100 Hz bis 100 MHz)

- Integrierter RMS-Jitter bei 20 GHz = 31 fs (ADC-SRV-Methode)

- PLL-Spezifikationen

- -239dBc/Hz normalisiertes In-Band-Phasenrauschen (Integer-Modus)

- -287dBc/Hz normiertes 1/f-Phasengrundrauschen

- 625 MHz maximale Phasen-/Frequenzdetektor-Eingangsfrequenz

- 4,5 GHz Referenzeingangsfrequenz

- -90dBc typische Störung fPFD

- Schnelle VCO-Kalibrierzeit von <>

- <100 μs="">

- -156dBc/Hz Phasenrauschboden bei 20 GHz

- Verweis auf die Spezifikationen zur Ausgangsverzögerung

- 0,06ps/°C Temperaturkoeffizient der Laufzeitverzögerung

- <1 ps="">

- Multichip-Ausgangsphasenausrichtung

- Stromversorgungen: 3,3 V und 5 V

- Unterstützung für ADIsimPLL™ Schleifenfilter-Design-Tool

- 7 mm × 7 mm, 48-polige LGA

- -40 °C bis +105 °C Betriebstemperatur

Applikationen

- Hochleistungs- Wechselrichter-Taktung

- Drahtlose Infrastrukturen (MC-GSM, 5 G 6 G)

- Prüfung und Messung

Funktionales Blockdiagramm